发布时间: 2024-06-14 13:52:43 来源:电竞比分-存储调理

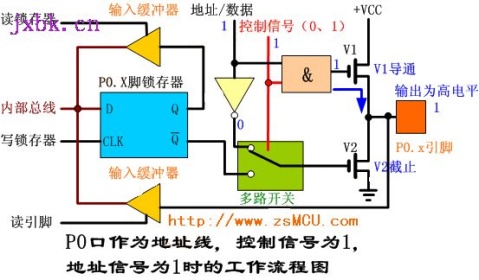

由上图可见,P0端口由锁存器、输入缓冲器、切换开关、一个与非门、一个与门及场效应管驱动电路构成。

先看输入缓冲器:在P0口中,有两个三态的缓冲器,在其的输出端可以是高电平、低电平,同时还有一种就是高阻状态(或称为禁止状态),上面一个是读锁存器的缓冲器,下面一个是读引脚的缓冲器,读取P0.X引脚上的数据,要使这个三态缓冲器有效,引脚上的数据才会传输到内部数据总线上。

D锁存器:在51单片机的32根I/O口线中都是用一个D触发器来构成锁存器的。D端是数据输入端,CP是控制端(也就是时序控制信号输入端),Q是输出端,Q非是反向输出端。

多路开关:在51单片机中,不需要外扩展存储器时,P0口可当作通用的输入输出端口(即I/O)使用,对于8031(内部没有ROM)的单片机或者编写的程序超过了单片机内部的存储器容量,需要外扩存储器时,P0口就作为地址/数据总线使用。这个多路选择开关就是用于选择是做为普通I/O口使用还是作为数据/地址总线使用的选择开关了。当多路开关与下面接通时,P0口是作为普通的I/O口使用的,当多路开关是与上面接通时,P0口是作为地址/数据总线使用的。

输出驱动部份:P0口的输出是由两个MOS管组成的推拉式结构,也就是说,这两个MOS管一次只能导通一个,当V1导通时,V2就截止,当V2导通时,V1截止。

P0口作为I/O端口使用时,多路开关的控制信号为0(低电平),V1管截止,多路开关是与锁存器的Q非端相接的(即P0口作为I/O口线使用)。作为地址/数据线使用时,多路开关的控制信号为1,V1管由地址/数据线决定,多路开关与地址/数据线连接。

1、I/O输出工作过程:当写锁存器信号CP有效,数据总线的信号锁存器的输入端D锁存器的反向输出Q非端多路开关V2管的栅极V2的漏极到输出端P0.X。这时多路开关的控制信号为低电平0,V1管是截止的,所以作为输出口时,P0是漏极开路输出,类似于OC门,当驱动上接电流负载时,需要外接上拉电阻。

控制信号为1,地址信号为“0”时,与门输出低电平,V1管截止;反相器输出高电平,V2管导通,输出引脚的地址信号为低电平。

反之,控制信号为“1”、地址信号为“1”,“与门”输出为高电平,V1管导通;反相器输出低电平,V2管截止,输出引脚的地址信号为高电平。请看下图(兰色字体为电平):

可见,在输出“地址/数据”信息时,V1、V2管是交替导通的,负载能力很强,可以直接与外设存储器相连,无须增加总线、作为数据总线的输出过程

如果该指令是输出数据,如MOVX @DPTR,A(将累加器的内容通过P0口数据总线传送到外部RAM中),则多路开关“控制”信号为1,“与门”解锁,与输出地址信号的工作流程类似,数据据由“地址/数据”线反相器V2场效应管栅极V2漏极输出。

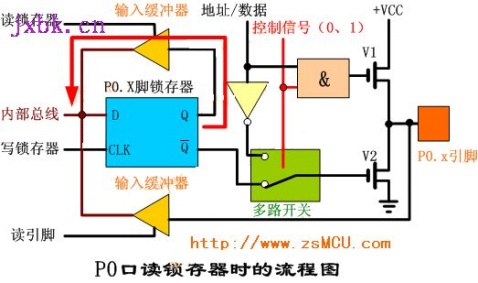

通过打开读锁存器三态缓冲器读取锁存器输出端Q的状态,请看下图(红色箭头):

时,P0口输出低8位地址信息后,将变为数据总线,以便读指令码(输入)。在取指令期间,“控制”信号为“0”,V1管截止,多路开关也跟着转向锁存器反相输出端Q非;CPU自动将0FFH(11111111,即向D锁存器写入一个高电平1)写入P0口锁存器,使V2管截止,在读引脚信号控制下,通过读引脚三态门电路将指令码读到内部总线,这样的一个过程和I/O读引脚过程是一样的。在输入状态下,从锁存器和从引脚上读来的信号一般是一致的,但也有例外。例如,当从内部总线输出低电平后,锁存器Q=0,Q非=1,场效应管T2开通,端口线呈低电平状态。此时无论端口线上外接的信号是低电乎还是高电平,从引脚读入单片机的信号都是低电平,因而不能正确地读入端口引脚上的信号。又如,当从内部总线输出高电平后,锁存器Q=1,Q非=0,场效应管T2截止。如外接引脚信号为低电平,从引脚上读入的信号就与从锁存器读入的信号不同。为此,8031单片机在对端口P0一P3的输入操作上,有如下约定:为此,

单片机在对端口P0一P3的输入操作上,有如下约定:凡属于读-修改-写方式的指令,从锁存器读入信号,其它指令则从端口引脚线上读入信号。读-修改-写指令的特点是,从端口输入(读)信号,在单片机内加以运算(修改)后,再输出(写)到该端口上。这样安排的原因主要在于读-修改-写指令需要得到端口原输出的状态,修改后再输出,读锁存器而不是读引脚,能够尽可能的防止因外部电路的原因而使原端口的状态被读错。当P0作为地址/数据总线使用时,在读指令码或输入数据前,CPU自动向P0口锁存器写入0FFH,破坏了P0口原来的状态。因此,不能再作为通用的I/O端口。在系统模块设计时务必注意,即程序中不能再含有以P0口作为操作数(包含源操作数和目的操作数)的指令。二、P1端口的结构及工作原理

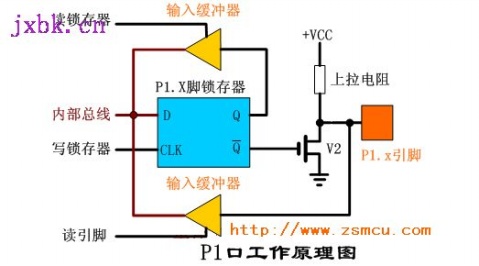

由图可见,P1端口与P0端口的主要差别在于,P1端口用内部上拉电阻R代替了P0端口的场效应管T1,并且输出的信息仅来自内部总线。由内部总线输出的数据经锁存器反相和场效应管反相后,锁存在端口线端口是具有输出锁存的静态口。要正确地从引脚上读入外部信息,必须先使场效应管关断,以便由外部输入的信息确定引脚的状态。为此,在作引脚读入前,必须先对该端口写入l。具有这种操作特点的输入/输出端口,称为准双向I/O口。8051单片机的P1、P2、P3都是准双向口。P0端口由于输出有三态功能,输入前,端口线已处于高阻态,无需先写入l后再作读操作。单片机复位后,各个端口已自动地被写入了1,此时,可直接作输入操作。如果在应用端口的过程中,已向P1一P3端口线,则再要输入时,必须先写1后再读引脚,才能得到正确的信息。此外,随输入指令的不同,P1端口也有读锁存器与读引脚之分。

由图可见,P2端口在片内既有上拉电阻,又有切换开关MUX,所以P2端口在功能上兼有P0端口和P1端口的特点。这主要体现在输出功能上,当切换开关向下接通时,从内部总线输出的一位数据经反相器和场效应管反相后,输出在端口引脚线上;当多路开关向上时,输出的一位地址信号也经反相器和场效应管反相后,输出在端口引脚线单片机必须外接程序存储器才能构成应用电路(或者我们的应用电路扩展了外部存储器),而P2端口就是用来周期性地输出从外存中取指令的地址(高8位地址),因此,P2端口的多路开关总是在进行切换,分时地输出从内部总线来的数据和从地址信号线端口是动态的I/O端口。输出数据虽被锁存,但不是稳定地出现在端口线上。其实,这里输出的数据往往也是一种地址,仅仅是外部RAM的高8位地址。

②执行MOVX指令时,还输出外部RAM的高位地址,故称P2端口为动态地址端口。

即然P2口可当作I/O口使用,也可当作地址总线使用,下面我们就分析下它的两种工作状态。

当没有外部程序存储器或虽然有外部数据存储器,但容易不大于256B,即不需要高8位地址时(在这样的一种情况下,不能通过数据地址寄存器DPTR读写外部数据存储器),P2口可以I/O口使用。这时,“控制”信号为“0”,多路开关转向锁存器同相输出端Q,输出信号经内部总线锁存器同相输出端Q反相器V2管栅极V2管9漏极输出。

由于V2漏极带有上拉电阻,能够给大家提供一定的上拉电流,负载能力约为8个TTL与非门;作为输出口前,同样需要向锁存器写入“1”,使反相器输出低电平,V2管截止,即引脚悬空时为高电平,防止引脚被钳位在低电平。读引脚有效后,输入信息经读引脚三态门电路到内部数据总线、作为地址总线口作为地址总线时,“控制”信号为1,多路开关车向地址线(即向上接通),地址信息经反相器V2管栅极漏极输出。由于P2口输出高8位地址,与P0口不同,无须分时使用,因此P2口上的地址信息(程序存储器上的A15~A8)功数据地址寄存器高8位DPH保存时间长,无须锁存。

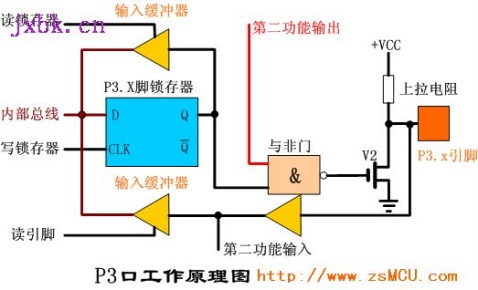

上图可见,P3端口和Pl端口的结构相似,区别仅在于P3端口的各端口线有两种功能选择。当处于第一功能时,第二输出功能线,此时,内部总线信号经锁存器和场效应管输入/输出,其作用与P1端口作用相同,也是静态准双向I/O端口。当处于第二功能时,锁存器输出1,通过第二输出功能线输出特定的内含信号,在输入方面,即能够最终靠缓冲器读入引脚信号,还能够最终靠替代输入功能读入片内的特定第二功能信号。由于输出信号锁存并且有双重功能,故P3端口为静态双功能端口。

在应用中,如不设定P3端口各位的第二功能(WR,RD信号的产生不用设置),则P3端口线自动处于第一功能状态,也就是静态I/O端口的工作状态。在更多的场合是根据应用的需要,把几条端口线设置为第二功能,而另外几条端口线处于第一功能运作时的状态。在这种情况下,不宜对P3端口作字节操作,需采用位操作的形式。